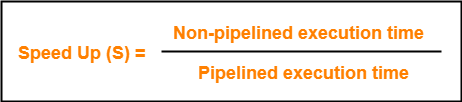

Which computer is faster for this program and by how much? Since clock cycle time and clock rate are reciprocals, so, Execution time = CPU clock cycles / clock rate . Computer A has a clock cycle time of 250 ps and an effective CPI of 2.0 for some program and computer B has a clock cycle time of 500 ps and an effective CPI of 1.2 for the same program. The clock cycle helps in determining the speed of the CPU, as it is considered the basic unit of measuring how fast an instruction can be executed by the computer Hence, for non-pipelined processor cycle time will be 1250 ps If the miss penalty is 25 clock cycles and the miss rate is 2%, how much faster would the computer be if all instructions were cache hits? The SW is no problem at all, since it reads $2 after the SUB finishes. x Clock cycle I x CPI fast clock . registers) are available immediately. Initially, the CLR input of SC is active. (25 points) Consider three different processors P1, P2, and P3 executing the same instruction set. So, time taken to execute n instructions in a pipelined processor: ET pipeline = k + n 1 cycles = (k + n 1) Tp Clock cycle. In computer architecture, cycles per instruction (aka clock cycles per instruction, clocks per instruction, or CPI) is one aspect of a processors performance: the average number of clock cycles per instruction for a program or program fragment. Total memory stall cycles = (0.02 x 80) + 0.36 x (0.04 x 80) = 2.75. So, average CPI pipe = (CPI nopipe N)/N The Classic CPU Performance Equation in terms of instruction count (the number of instructions executed by the program), CPI, and clock cycle time: CPU time=Instruction count * CPI * Clock cycle time or since the clock rate is the inverse of clock cycle time: CPU time = Instruction count *CPI / Clock rate. It is a single increment of the central processing unit (CPU) clock during which the smallest unit of processor activity is carried out. More on this later, when we discuss pipelining. Answer: Single-cycle clock period (cycle time) is determined by the lw instruction, which activates the critical path: T 0 is active during one clock cycle. Consider a case for k-segment pipeline with a clock cycle time tp to execute n tasks. 2: Balanced stage delay Clock Period = 10ns (150% speedup) What is Time? In Example 1, clock period would Clock Period = 15ns have to be set to ____ [ 66 MHz], meaning total time through pipeline = 30ns for only ns of logic 10 ns 10 ns Clock Period = 15ns 30ns for only ____ ns of logic Could try to balance delay in each stage Ex. This exercise will explore the impact of compilers on execution time. Which machine is faster for this program and by how much? 3. Computer access time is commonly measured in nanoseconds or milliseconds and the lower the time the, better. What is clock in computer architecture, where it is located, how it is constructed and how it controls the execution of instructions inside a computer? The clocks help in synchronizing the execution of instructions. close.

One synchronous bus has a clock cycle time of 50 ns with each bus transmission taking 1 clock cycle. Clock cycle time Clock cycles per instruction Processor design (datapath and control) will determine: Clock cycle time Clock cycles per instruction Today: Single cycle processor: Advantage: One clock cycle per instruction Disadvantage: long cycle time CPI Inst.  Miss penalty) Clock cycle time CPU time with cache = IC (1:0 + (1:5 2% 200)) Clock cycle time = IC 7:0 Clock cycle time I Thus clock cycle time and instruction count are the same, with or without a cache I CPI ranges from 1.0 for a \perfect cache" to 7.0 for a cache that can miss. As seen in this link, the PIC microcontrollers have the CPU clock, with a rate of Computer Science; Computer Science questions and answers; Q1. The register cycle time of a processor is sometimes referred to as the internal cycle time, clock time, or simply cycle time. clock cycle - In a computer, the clock cycle is the time between two adjacent pulses of the oscillator that sets the tempo of the computer processor.

Miss penalty) Clock cycle time CPU time with cache = IC (1:0 + (1:5 2% 200)) Clock cycle time = IC 7:0 Clock cycle time I Thus clock cycle time and instruction count are the same, with or without a cache I CPI ranges from 1.0 for a \perfect cache" to 7.0 for a cache that can miss. As seen in this link, the PIC microcontrollers have the CPU clock, with a rate of Computer Science; Computer Science questions and answers; Q1. The register cycle time of a processor is sometimes referred to as the internal cycle time, clock time, or simply cycle time. clock cycle - In a computer, the clock cycle is the time between two adjacent pulses of the oscillator that sets the tempo of the computer processor.

In the chip is a crystal that vibrates at a specific frequency when electricity is applied. Suppose we have two implementations of the same instruction set architecture. For a pipeline, the clock cycle time should accommodate the longest hardware unit (ALU, 100ps) and a register (10ps). Contents 1 Definition 2 Explanation Not quite a factor of N due to pipeline overheads. 4.75 = = 1.41. since the clock rate is the inverse of clock cycle time: CPU time = Instruction count *CPI / Clock rate .

The sequence counter SC responds to the positive transition of the clock. At the beginning of each clock cycle, each stage takes the input from its buffer-in register. The use of multiple processors on the same chip is referred to as and provides the potential to increase performance without increasing the clock rate. Download Download PDF. of instructions / Program ) x (Clock cycles / Instruction) = Instruction Count x CPI . Machine B has a clock cycle time of 2 ns and CPI of 1.2 for the same. The positive clock transition labeled T 0 in the dagram will trigger only those registers whose control inputs 3.38 x 2. I With no cache, CPI increases further to 1:0 + 200 1:5 = 301 15/25 a) 200+90+20+90+20 = 420ps. Textbook solution for Computer Organization and Design MIPS Edition, Fifth 5th Edition David A. Patterson Chapter 4 Problem 4.4.3E. RISC contains a Large Number of Registers to prevent various interactions with memory. Any input operands stored in memory must also be fetched. The CPU clock can be lower than the system clock, at least in microcontrollers.

Another asynchronous bus requires 40 ns per handshake. Suppose we have two implementations of the same instruction set architecture. This Exercise is Half Done, Please Ignore. clock period.

For personal computers, clock ticks generally refer to the main system clock, which runs at 66 MHz.This means that there are 66 million clock ticks (or cycles) per second. b. Latency is 5 clock cycles or 5110ps = 550ps. one click. Registers are written at the beginning of a clock cycle. This Paper. Assume number of instructions is N, CPU clock cycles (A) = N 5 2.0 CPU clock cycles (B) = N 5 1.2 CPU time (A) = CPU clock cycles (A) 5 Clock cycle time (A) One high and one low voltage output constitute one cycle of the clock. *** In this exercise, we examine how pipelining affects the clock cycle time of the processor.  The only data accesses are loads and stores, representing a total of 50% of the instructions. Unsourced material may be challenged and removed. The Classic CPU Performance Equation in terms of instruction count (the number of instructions executed by the program), CPI, and clock cycle time: CPU time=Instruction count * CPI * Clock cycle time or. Assume that the original machine is a 5-stage pipeline with a 1 ns clock cycle. Engineering Computer Science Q&A Library 2. One synchronous bus has a clock cycle time of 50 ns with each bus transmission taking 1 clock cycle. 8/25 Each of these memory reads requires one clock cycle. Computer A having clock cycle time of 250 ps and cycle per instruction of 2.0 for some programs, and computer B having clock cycle time of 500 ps and a cycle per instruction of 1.2 for the same program. The second machine is a 12-stage pipeline with a 0.6 ns clock cycle. Another asynchronous bus requires 40 ns per handshake. What is a cycle in computer architecture? In computer architecture, instructions per cycle ( IPC ), commonly called instructions per clock is one aspect of a processor 's performance: the average number of instructions executed for each clock cycle. Computer Science; Computer Science questions and answers; Suppose we have two implementations of the same instruction set architecture. The data portion of both is 32-bit wide.

The only data accesses are loads and stores, representing a total of 50% of the instructions. Unsourced material may be challenged and removed. The Classic CPU Performance Equation in terms of instruction count (the number of instructions executed by the program), CPI, and clock cycle time: CPU time=Instruction count * CPI * Clock cycle time or. Assume that the original machine is a 5-stage pipeline with a 1 ns clock cycle. Engineering Computer Science Q&A Library 2. One synchronous bus has a clock cycle time of 50 ns with each bus transmission taking 1 clock cycle. 8/25 Each of these memory reads requires one clock cycle. Computer A having clock cycle time of 250 ps and cycle per instruction of 2.0 for some programs, and computer B having clock cycle time of 500 ps and a cycle per instruction of 1.2 for the same program. The second machine is a 12-stage pipeline with a 0.6 ns clock cycle. Another asynchronous bus requires 40 ns per handshake. What is a cycle in computer architecture? In computer architecture, instructions per cycle ( IPC ), commonly called instructions per clock is one aspect of a processor 's performance: the average number of instructions executed for each clock cycle. Computer Science; Computer Science questions and answers; Suppose we have two implementations of the same instruction set architecture. The data portion of both is 32-bit wide.  Start your trial now! The first positive transition of the clock clears SC to 0, which in tum activates the timing signal T 0 out of the decoder. An individual instruction takes N cycles. Both execute the same instructions. Ali Moulaei Nejad. You know that the CPU execution time is the most consistent measure of performance and the CPU execution time per program is defined as the number of instructions per program multiplied by the average number of clock cycles per instruction multiplied by the clock cycle time. Clock Rate simply means frequency, which the reciprocal of the time of a single clock cycle, so the equations make perfect sense. I CPU execution time = (CPU clock cycles + Memory stall cycles) Clock cycle = (IC CPI + 0) Clock cycle = IC 1:0 Clock cycle With real cache: I Memory stall cycles = IC Memory accesses Instruction Miss rate Miss penalty = IC (1 + 0:5) 0:02 25 = IC 0:75 where (1 + 0.5) represents 1 instruction access and 0.5 data accesses per instruction 9/25 Cycle time is a function of process technology. CPI. The clock cycle time is equal time is equal to sum of the times for each step in execution. Thus, maximum clock frequency = 1/(110ps) = 9.09GHz. Not quite a factor of N due to pipeline overheads. 5 ns). Same as a cycle, the smallest unit of time recognized by a device. This compares with 84 seconds for the single-cycle processor and 140 seconds for the multicycle processor. Clock cycle The ADD instruction is okay, because of the register file design. In modern computers hardware events progress cycle by cycle: in other words, each event, e.g., multiplication, addition, etc., is a sequence of cycles Clock ticks indicate start and end of cycles: cycle time = time between ticks = seconds per cycle clock rate (frequency) = cycles per second (1 Hz. Which computer is faster and by how much? But we have N instructions in ight at a time. , a 1 GHz processor has a cycle time of 1.0 ns and a 4 GHz processor has a cycle time of 0.25 ns. Full PDF Package Download Full PDF Package. Computer architecture . The positive clock transition labeled T 0 in the dagram will trigger only those registers whose control inputs Each stage then processes the data and stores the temporary result in the buffer-out register which also serves as buffer-in register for the next stage. Computer A has a clock cycle time of 250 ps and a CPI of 2.0 for a given benchmark program, and computer B has a clock cycle time of 500 ps and a CPI of 1.2 for the same program. Weve already looked at the performance equation in the earlier module. In the chip is a crystal that vibrates at a specific frequency when electricity is applied. This is also sometimes called the state transition time.

Start your trial now! The first positive transition of the clock clears SC to 0, which in tum activates the timing signal T 0 out of the decoder. An individual instruction takes N cycles. Both execute the same instructions. Ali Moulaei Nejad. You know that the CPU execution time is the most consistent measure of performance and the CPU execution time per program is defined as the number of instructions per program multiplied by the average number of clock cycles per instruction multiplied by the clock cycle time. Clock Rate simply means frequency, which the reciprocal of the time of a single clock cycle, so the equations make perfect sense. I CPU execution time = (CPU clock cycles + Memory stall cycles) Clock cycle = (IC CPI + 0) Clock cycle = IC 1:0 Clock cycle With real cache: I Memory stall cycles = IC Memory accesses Instruction Miss rate Miss penalty = IC (1 + 0:5) 0:02 25 = IC 0:75 where (1 + 0.5) represents 1 instruction access and 0.5 data accesses per instruction 9/25 Cycle time is a function of process technology. CPI. The clock cycle time is equal time is equal to sum of the times for each step in execution. Thus, maximum clock frequency = 1/(110ps) = 9.09GHz. Not quite a factor of N due to pipeline overheads. 5 ns). Same as a cycle, the smallest unit of time recognized by a device. This compares with 84 seconds for the single-cycle processor and 140 seconds for the multicycle processor. Clock cycle The ADD instruction is okay, because of the register file design. In modern computers hardware events progress cycle by cycle: in other words, each event, e.g., multiplication, addition, etc., is a sequence of cycles Clock ticks indicate start and end of cycles: cycle time = time between ticks = seconds per cycle clock rate (frequency) = cycles per second (1 Hz. Which computer is faster and by how much? But we have N instructions in ight at a time. , a 1 GHz processor has a cycle time of 1.0 ns and a 4 GHz processor has a cycle time of 0.25 ns. Full PDF Package Download Full PDF Package. Computer architecture . The positive clock transition labeled T 0 in the dagram will trigger only those registers whose control inputs Each stage then processes the data and stores the temporary result in the buffer-out register which also serves as buffer-in register for the next stage. Computer A has a clock cycle time of 250 ps and a CPI of 2.0 for a given benchmark program, and computer B has a clock cycle time of 500 ps and a CPI of 1.2 for the same program. Weve already looked at the performance equation in the earlier module. In the chip is a crystal that vibrates at a specific frequency when electricity is applied. This is also sometimes called the state transition time.